Un team di ingegneri provenienti da Stanford University, Carnegie Mellon University, University of Pennsylvania e MIT, in collaborazione con SkyWater Technology, la più grande fonderia di semiconduttori “pure play” con sede esclusivamente negli Stati Uniti, ha realizzato un nuovo chip 3D monolitico che potrebbe segnare un punto di svolta nell’hardware per l’intelligenza artificiale.

Secondo i ricercatori, questa nuova architettura non solo migliora drasticamente le prestazioni rispetto ai chip tradizionali, ma rappresenta anche una strada concreta per rilanciare l’innovazione dei semiconduttori su suolo statunitense.

Dal chip piatto al chip 3D “a grattacielo”

La maggior parte dei processori attuali è bidimensionale: transistor, memoria e logica sono distribuiti su un’unica superficie. Il nuovo prototipo, invece, cresce in verticale.

Il concetto è semplice quanto potente:

- strati ultrasottili di circuiti vengono impilati come i piani di un edificio,

- connessioni verticali ad alta densità funzionano come ascensori rapidissimi, capaci di spostare enormi quantità di dati in pochissimo tempo.

Questo approccio consente di posizionare memoria e unità di calcolo molto più vicine, riducendo drasticamente i colli di bottiglia che affliggono i chip tradizionali. Nei test hardware e nelle simulazioni, il chip 3D ha superato le controparti 2D di circa un ordine di grandezza.

Il vero nemico dell’AI moderna: la “memory wall”

Modelli di intelligenza artificiale come ChatGPT o Claude non sono limitati tanto dalla potenza di calcolo quanto dalla velocità con cui riescono a spostare dati tra memoria e processore.

Nei chip 2D:

- la memoria è limitata e distribuita,

- i dati devono attraversare percorsi lunghi e congestionati,

- le unità di calcolo restano spesso in attesa.

Questo problema è noto come memory wall: la CPU (o l’acceleratore AI) è più veloce di quanto i dati riescano ad arrivare.

Per anni l’industria ha cercato di aggirare il problema miniaturizzando sempre di più i transistor. Ma oggi questa strategia si sta scontrando con limiti fisici ben noti, il cosiddetto miniaturization wall.

Il chip 3D monolitico nasce proprio per superare entrambi questi muri.

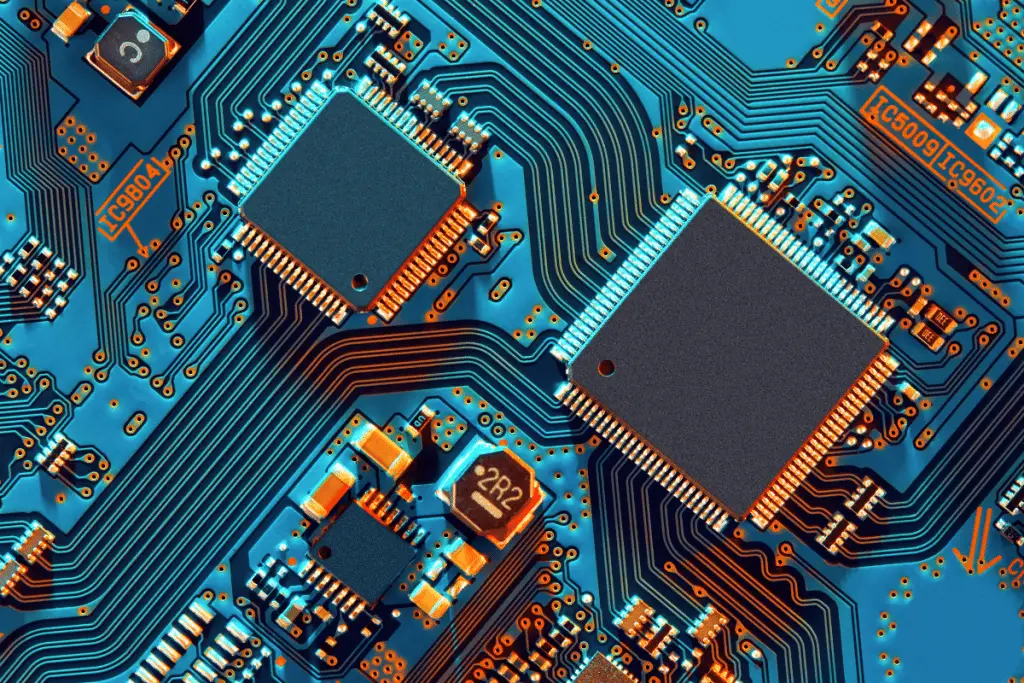

Perché “monolitico” fa la differenza

In passato si è già tentato di realizzare chip 3D semplicemente impilando chip separati. Una soluzione utile, ma con un grosso limite: le connessioni tra i livelli sono poche, grossolane e spesso diventano nuovi colli di bottiglia.

Il team ha invece adottato un approccio più radicale:

ogni strato viene costruito direttamente sopra il precedente, in un unico processo produttivo continuo. Questo metodo, chiamato integrazione 3D monolitica, utilizza temperature sufficientemente basse da non danneggiare i circuiti sottostanti.

Il risultato è:

- densità molto più elevata,

- connessioni verticali estremamente numerose,

- comunicazione tra memoria e logica molto più rapida ed efficiente.

Elemento chiave: l’intero processo è stato realizzato in una fonderia commerciale statunitense, non in un laboratorio sperimentale.

Prestazioni chip 3d: non solo più veloci, ma anche più efficienti

Nei primi test, il prototipo ha mostrato prestazioni circa 4 volte superiori rispetto a chip 2D equivalenti. Le simulazioni indicano che, aumentando il numero di strati, i miglioramenti potrebbero arrivare fino a 12 volte su carichi di lavoro reali di intelligenza artificiale, inclusi quelli basati sul modello open source LLaMA di Meta.

Ma il dato forse più interessante riguarda l’efficienza energetica e s econdo i ricercatori, questa architettura offre una strada realistica verso miglioramenti da 100 a 1.000 volte dell’Energy Delay Product (EDP), una metrica che combina velocità ed energia consumata.

In altre parole: più throughput, meno energia per operazione.

Una combinazione sempre più difficile da ottenere con i chip piatti tradizionali.

Un segnale strategico, non solo tecnologico

Il valore di questo progetto non è solo tecnico. Dimostrare che chip 3D monolitici avanzati possono essere progettati e prodotti negli Stati Uniti fornisce un modello concreto per una nuova fase di sovranità tecnologica nel settore dei semiconduttori.

Secondo il team, il passaggio al 3D monolitico richiederà anche una nuova generazione di ingegneri, formati su queste tecnologie, proprio come accadde negli anni ’80 con l’esplosione dei circuiti integrati. Programmi come il Microelectronics Commons AI Hardware Hub stanno già lavorando in questa direzione.

Perché conta davvero

Come ha spiegato uno dei responsabili del progetto, questi risultati non riguardano solo le prestazioni pure: riguardano la capacità di innovare più velocemente, reagire più in fretta alle esigenze dell’AI moderna e definire il futuro dell’hardware, invece di inseguirlo.

Se il paradigma 2D sta arrivando al capolinea, il messaggio è chiaro: il futuro dei chip – e dell’intelligenza artificiale – sale in verticale.