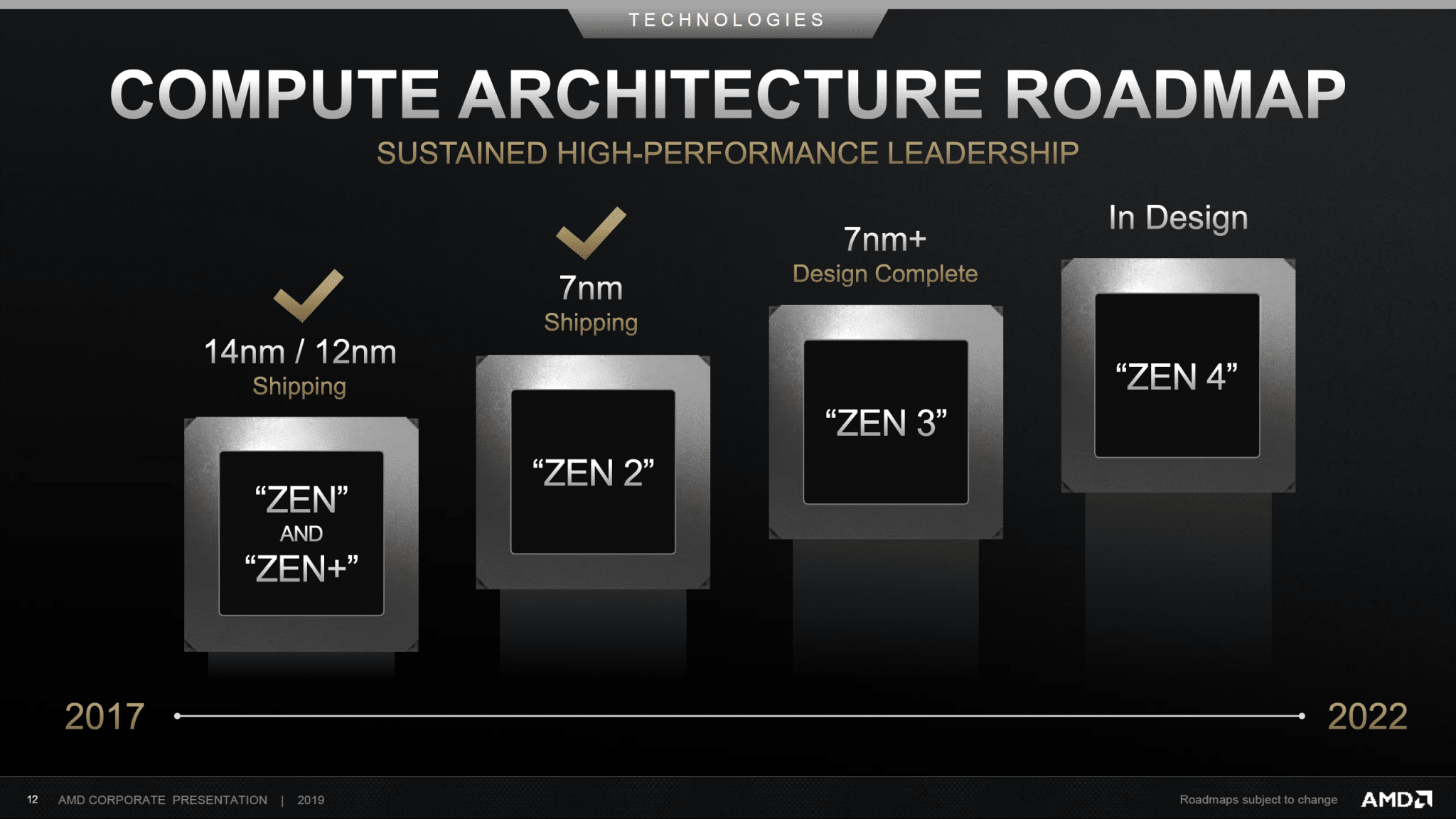

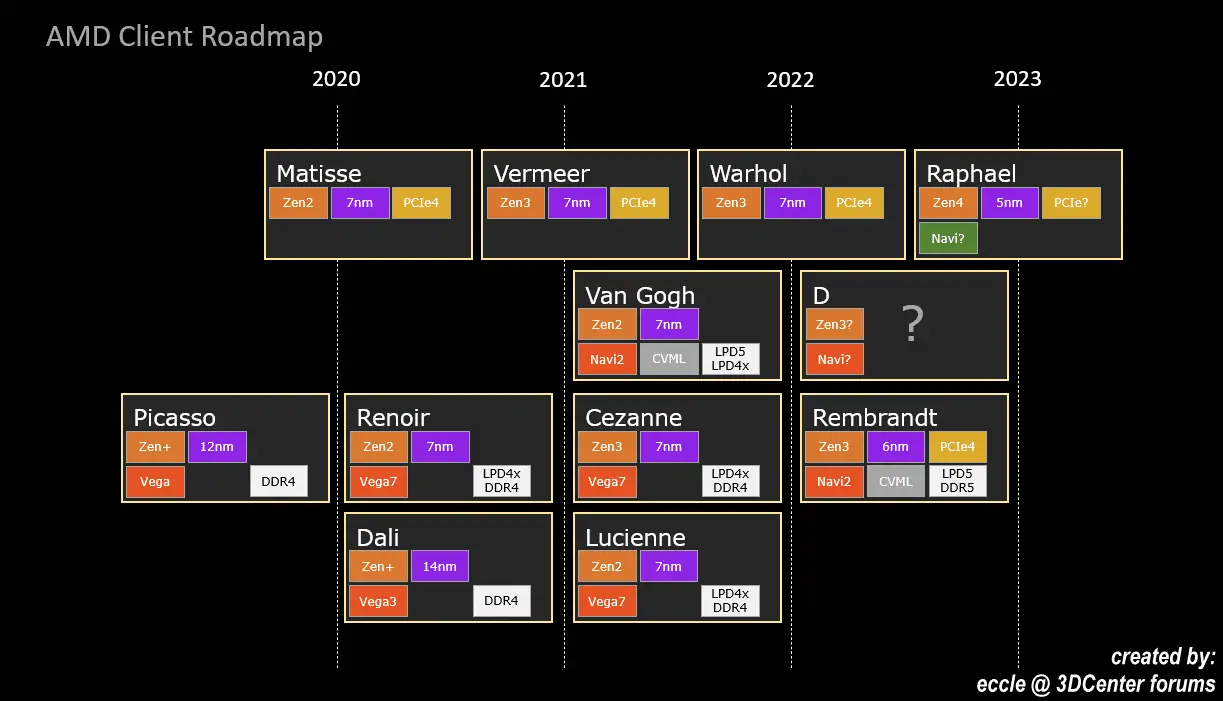

Il termine APU (unità di elaborazione accelerata) o Fusion, o Fusion APU, fu registrato da AMD nel 2011 ed era basato sull’architettura Picasso, ora potremmo vedere AMD Van Gogh, almeno secondo un registro di avvio del kernel Linux pubblicato dall’azienda stessa.

Se le informazioni trapelate dovessero rivelarsi corrette, l’imminente APU di AMD potrebbe offrire un enorme aumento dei carichi di lavoro ad alta intensità di memoria, come la grafica.

AMD Van Gogh è un’APU piuttosto enigmatica che si ritiene integri core per uso generico basati sulla microarchitettura Zen 2 e un motore grafico basato sull’architettura RDNA2, che lo rende simile al sistema personalizzato su chip (SoC) che AMD ha sviluppato per Xbox Series X di Microsoft e per PlayStation 5.

Il processore dovrebbe essere realizzato utilizzando la tecnologia di processo N7 di TSMC, sebbene queste informazioni non provengano da AMD, inoltre per aggiungere ancora un po’ di mistero, si diceva che il processore AMD Van Gogh fosse dotato di un sottosistema di memoria DDR5 ma che poi stranamente avesse perso questa capacità, ottenendo però il supporto LPDDR5.

Questo mese, uno degli ingegneri software di AMD ha pubblicato un registro di avvio del kernel Linux per l’APU quad-core AMD Van Gogh (contrassegnato come esempio AMD Eng: 100-000000405-03_35 / 24_N, famiglia: 0x17, modello: 0x90, stepping: 0x1) il quale afferma che il processore supporta un’interfaccia di memoria DDR5 a 256 bit.

Un’interfaccia di memoria a 256 bit non è una novità per le CPU desktop di fascia alta e per le console di gioco, ma per i tipici processori per PC client un’interfaccia DRAM così ampia è considerata eccessiva.

Nel frattempo, se AMD vuole offrire prestazioni grafiche rivoluzionarie con un’APU, un’interfaccia DDR5 a 256 bit potrebbe essere una scelta logica. Ciò che è alquanto illogico è usare quattro core Zen 2 per uso generico con un’APU di fascia alta.

Ulteriori dettagli sull’APU AMD Van Gogh ed i suoi 256 bit

Dal punto di vista del sistema operativo il tipo di memoria utilizzata dalla piattaforma non è molto importante, motivo per cui esistono CPU moderne che possono funzionare altrettanto bene sia con DDR4 che LPDDR4X.

L’interfaccia DDR5 tuttavia ha numerose somiglianze con quella LPDDR4, ma con un intervallo di indirizzamento diverso rispetto ai tipi di memoria esistenti, inoltre anche le LPDDR5 e le DDR5 condividono delle somiglianze.

È possibile che un sistema di sviluppo possa rilevare in modo errato LPDDR5 come DDR5 (specialmente con un BIOS di pre-produzione), e di conseguenza ciò potrebbe anche portare la scheda a rilevare più canali di memoria LPDDR5 a 16 bit o DDR5 a 32 bit come diversi canali DDR4 a 64 bit, mostrando una “interfaccia DDR5 a 256 bit”.

Fatta questa premessa, tornando al punto di partenza, l’interfaccia di memoria dell’APU AMD Van Gogh va a creare un nuovo dilemma e nuove incognite; data la CPU a 4 core, sospetto che questa non sia in realtà un’interfaccia DDR5 a 256 bit ma, molto probabilmente, è un’interfaccia a 128 bit, forse anche un’interfaccia a 64 bit ottimizzata per dispositivi mobili con LPDDR5.

Nel caso in cui mi dovessi sbagliare, potrebbe effettivamente essere un’APU con più larghezza di banda di memoria e una GPU più grande, e ciò sarebbe in qualche modo assurdo, ma tutto è possibile a questo punto.

La scheda madre di sviluppo utilizzata per eseguire l’APU AMD Van Gogh ha il nome in codice Chachani-VN, ma non si sa molto sulle sue specifiche.

Nel frattempo, ci sono altri nomi in codice della piattaforma Van Gogh rivelati in precedenza, tra cui Celadon (una piattaforma mobile FP6), Mytle (una piattaforma desktop AM4) e Artistic (una piattaforma desktop sconosciuta).

Di quelli che ti ho appena nominato, solo il Celadon è menzionato nel registro di avvio, quindi molto probabilmente abbiamo a che fare con una piattaforma mobile; tenendo presente che l’APU Van Gogh di AMD non è stata annunciata formalmente e AMD non commenta prodotti inediti, è quasi impossibile ottenere dettagli ufficiali sul processore, quindi si spera in qualche futuro leak e/o annuncio.